In this

article:

Source Code

License

Navigation:

HomeHardware

Software

Techniques

Controllers

Reviews

Index

Description

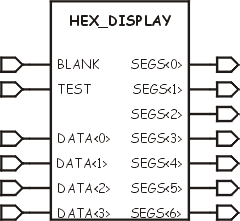

This is the first implementation of the hex display code. It follows what I considered at the time reasonable practices around writing VHDL code. However, when the hardware is inferred from this description, the synthesis tool ends up building a lot of extra hardware that isn’t needed to implement the display. In particular the if statements generate latches when we only need gates. See the discussion in the article.

The Source Code

--- HEX_DISPLAY Chuck McManis 8-Mar-2001 --- --- This is a driver for a 7 segment LED display. It converts a 4-bit nybble --- into a hexadecimal character 0-9a-f. Some letters are upper case others are --- lower case in an effort to distinguish them from numbers so b and 6 differ --- by the presence of the top segment being lit or not. (for example) --- library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity hex_display is Port ( value : in std_logic_vector(3 downto 0); blank : in std_logic; test : in std_logic; segs : out std_logic_vector(6 downto 0)); end hex_display; -- This is a good third project since it is simply combinatorial logic. When -- synthesized the selection statement (case) generates a decoder that takes -- four input lines and generates seven output lines. (the decimal point is -- not effected. If you want to get decimal point control, try adding -- another pin (dp) to the port description, and then you can assign it with -- a concurrent signal assignment architecture behavioral of hex_display is begin process (value, blank, test) is begin if (blank = '1') then segs <= "0000000"; elsif (test = '1') then segs <= "1111111"; else case value is when "0000" => segs <= "0111111"; -- 0 when "0001" => segs <= "0000110"; -- 1 when "0010" => segs <= "1011011"; -- 2 when "0011" => segs <= "1001111"; -- 3 when "0100" => segs <= "1100110"; -- 4 when "0101" => segs <= "1101101"; -- 5 when "0110" => segs <= "1111101"; -- 6 when "0111" => segs <= "0000111"; -- 7 when "1000" => segs <= "1111111"; -- 8 when "1001" => segs <= "1100111"; -- 9 when "1010" => segs <= "1110111"; -- A when "1011" => segs <= "1111100"; -- b when "1100" => segs <= "0111001"; -- c when "1101" => segs <= "1011110"; -- d when "1110" => segs <= "1111001"; -- E when others => segs <= "1110001"; -- F end case; end if; end process; end behavioral;

License

This work is licensed under a Creative Commons Attribution-NonCommercial 3.0 Unported License. You are free to play around with it and modify it but you are not licensed to use it for commercial purposes. Click the link above for more details on your rights under this license.